ساخت این تایمر راحت هستش. اما طرز کارش کمی پیچیده است، زیرا بر اساس استفاده از یک زمانسنج قابل برنامهریزی از نوع CD4541 طرح شده است.

با NE555 تأخیر زمانی طولانی، به دلیل جریان نشتی زیاد خازنهای شیمیایی با ظرفیت بسیار زیاد، مشکل و نامطمئن خواهد بود. البته امکان پذیر هست، اما نه دقیق هست و نه بسیار قابل اعتماد.

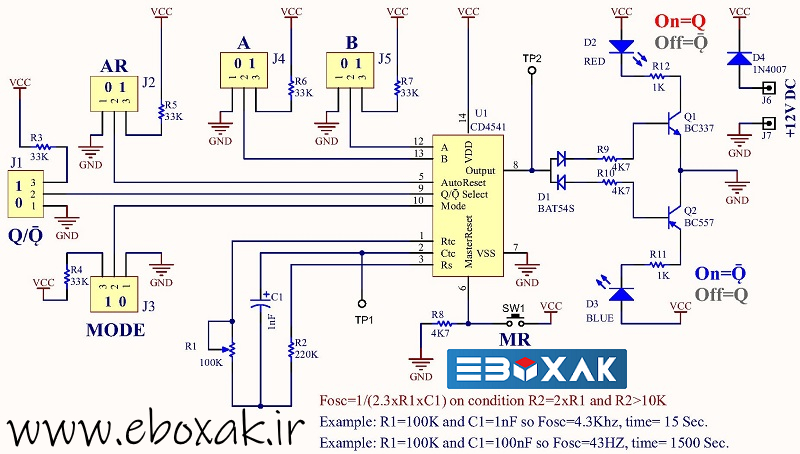

نمودار

CD4541 تایمر قابل برنامهریزی نامیده شده، زیرا برای نحوه عملکرد و قابلیت برنامهریزی آن، چندین پین در بدنه تعبیه شده است. پینهای Rtc(1), Ctc(2) و Rs(3) برای دسترسی به اسیلاتور داخلی هستند، که با افزودن دو مقاومت و یک خازن خارجی )در نمودار به نامهایR1, R2 و C1) پیکربندی میشوند.

فرکانس اسیلاتور داخلی به طور مستقیم با مقدار اجزای R1 و C1 که به ترتیب متصل به RTC و CTC هستند، وابسته است. برای عملکرد صحیح، مقاومت R2 متصل به RS باید حداقل دو برابر مقدار R1 باشد.

عملکرد پینها

اتو ریست AR Pin (5) - ورودی برای تعیین رفتار تایمر هنگام روشنشدن.

اگر این ورودی در حالت منطقی صفر باشد، تایمر به محض روشنشدن مدار، فعال میشود، حتی اگر دکمه شروع را فشار نداده باشید. اگر این ورودی در منطق 1 باشد ، تایمر با روشنشدن مدار شروع نمیشود، اما به محض فشار دادن دکمه Start فعال میشود.

Master Reset (6) - پین بازنشانی اصلی که برای حالت تایمر استفاده میشود. در این صورت به شکل پایینکش پیکربندی شده، و برای راه اندازی تایمر لحظهایی Hi میشود. البته پین ورودی AR (5) باید در منطق 1 یا Hi باشد.

Output (8) - پین خروجی عمومی ، که پالس خروجی روی آن تولید میشود. پلاریته پالس خروجی با حالت منطقی منتخب و اعمال شده به ورودی پین(9) Q / Ǭ تعیین میشود.

Q / Ǭ Select (9) - ورودی برای تنظیم پلاریته پالس خروجی زمان بندی شده.

اگر این ورودی درحالت صفر منطقی پیکربندی شود، پالس خروجی Low خواهد بود (خروجی درموقع فعالیت Low و درموقع بیکاری یا پایان کار High است). اگر این ورودی در حالت منطقی یک یا High پیکربندی شود، پالس خروجی High خواهد بود (خروجی موقع بیکاری در حالت Low، و درموقع فعالیت High است).

(10) Mode- ریخت موج خروجی

نوع حالت منطقی ورودی در این پین، نوع سیگنال ارائه شده در خروجی اصلی، پین Q (8) را تعیین میکند. اگر این ورودی در حالت منطقی یک باشد ، خروجی پین Q(8) یک سیگنال پریودیک خواهد بود که فرکانس آن برابر با فرکانس اسیلاتور، تقسیم بر 2 به توان N است. عدد N مربوط به تعداد مرحله تقسیم بر 2 داخلی است، و مقدار آن بستگی به وضعیت منتخب در پین های A (Pin12) و نیز B (Pin13) دارد. اگر این ورودی در حالت صفر منطقی باشد، خروجی Q (8) یک تک سیگنال (این پالس تایمینگ است) ارائه میدهد و به محض بازگشت به حالت آماده به کار، متوقف میشود.

پین های A(12) و B(13) - این پین ها حالت منطقی ورودیها، برای نسبت تقسیم فرکانس ورودی (در اینجا اسیلاتور داخلی)، یا همان عدد N را تعیین میکنند. N مربوط به تعداد مراحل تقسیم داخلی بر 2 است.

نکته : اما آی سی های موجود در بازار فعلی (مهر 1400) دارای N به میزان یک واحد کمتر می باشند. به طور مثال N=8 در دیتا شیت، در المان های خریداری شده بر اساس N=7 بودند.

If A = 0 and B = 0, then N = 13, divide by 8192 (2 power 13)

If A = 0 and B = 1, then N = 10, division by 1024 (2 power 10)

If A = 1 and B = 0, then N = 8, division by 256 (2 power 8)

If A = 1 and B = 1, then N = 16, division by 65536 (2 power 16)

اگر A=0 و B=0 باشد، در اینصورت N=13 بوده و لذا 2 به توان 13 مساوی عدد 8192 بوده و در نتیجه فرکانس پالس در پین خروجی شماره 8، معادل خارج قسمت فرکانس ایجاد شده با المان های خارجی متصل به پین های 1، 2 و 3، تقسیم بر عدد 8192 خواهد بود.

اگر A=0 و B=1 باشد، در اینصورت N=10 بوده و لذا 2 به توان 10 برابر عدد 1024 خواهد بود.

اگر A=1 و B=0 باشد، در اینصورت N=8 بوده و لذا 2 به توان 13 برابر عدد 256 خواهد بود.

اگر A=1 و B=1 باشد، در اینصورت N=16 بوده و لذا 2 به توان 13 برابر عدد 65536 خواهد بود.

هرچه ضریب تقسیم بیشتر باشد، طول زمان پالس خروجی برای همان فرکانس نوسانساز طولانیتر است. من به نوبه خود ترجیح میدهم از حداکثر ضریب تقسیم استفاده کنم تا پالسهای طولانی با مقادیر کمتری از اجزا امکانپذیر باشد.

خلاصهایی از حالتهای ممکن

برای تعیین المانها، مطابق عملکرد مورد نیازم، جدولی مختصر تهیه کردم. رفتار مدار در لحظه روشنشدن بدین صورت به دست میآید، T ثابت زمان، زمانبندی (در حالت تایمر) یا پریود (در حالت اسیلاتور) را بیان میکند. توجه داشته باشید که در این مقاله نحوه عملکرد مدار به عنوان تایمر و نه اسیلاتور ذکر شده است. بنابراین، اتصال پین 10 به زمین ضروری است.

Master Reset (6) |

A |

B |

Auto Reset (5) |

Q/Ǭ Select (9) |

mode (10) |

Circuit behavior |

|

|

|

0 |

0 (pos) |

0 (time) |

خروجی بعد از T فعال میشود و فعال می ماند (نکته 1) |

|

|

|

0 |

0 (pos) |

1 (osc) |

خروجی پس از T روشن میشود و چشمک می زند |

|

|

|

0 |

1 (neg) |

0 (time) |

خروجی بلافاصله روشن میشود و بعد از T خاموش میشود (نکته 1) |

|

|

|

0 |

1 (neg) |

1 (osc) |

خروجی بلافاصله فعال میشود و سپس چشمک می زند |

|

|

|

1 |

0 (pos) |

0 (time) |

خروجی بلافاصله فعال میشود و فعال باقی می ماند |

|

|

|

1 |

0 (pos) |

1 (osc) |

خروجی پس از T فعال میشود و سپس چشمک می زند |

|

|

|

1 |

1 (neg) |

0 (time) |

خروجی بلافاصله روشن میشود و بعد از T خاموش میشود (نکته 2) |

|

|

|

1 |

1 (neg) |

1 (osc) |

خروجی بلافاصله روشن میشود و سپس چشمک می زند |

نکته 1: این دو مورد بدون شک بیشترین استفاده را خواهند داشت.

نکته 2: خیلی این رفتار را مفید نمیبینم ، به نظر من خروجی به طور معمول باید در حالت منطقی بالا باقی بماند.

در صورت تمایل تجربیات استفاده از این مدار را ذیل این فرسته به اشتراک بگزارید.

دیدگاهها

هیچ نظری هنوز ثبت نشده است.